概述

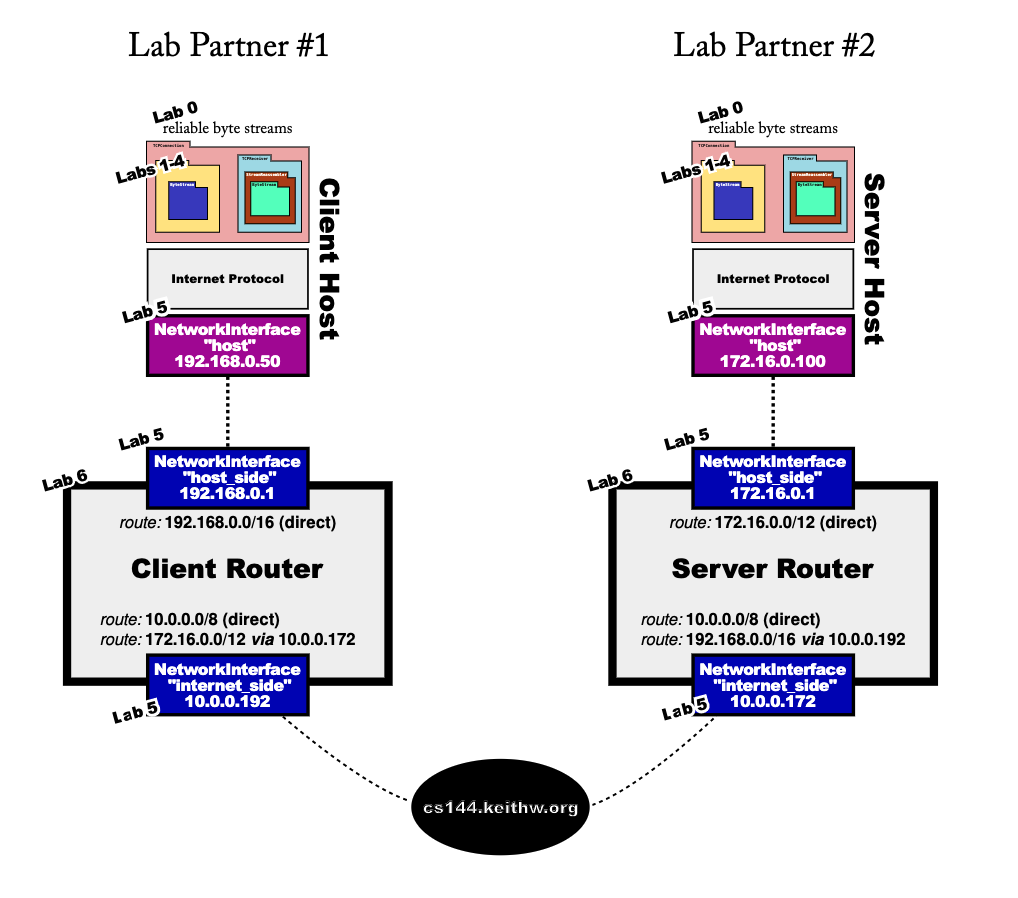

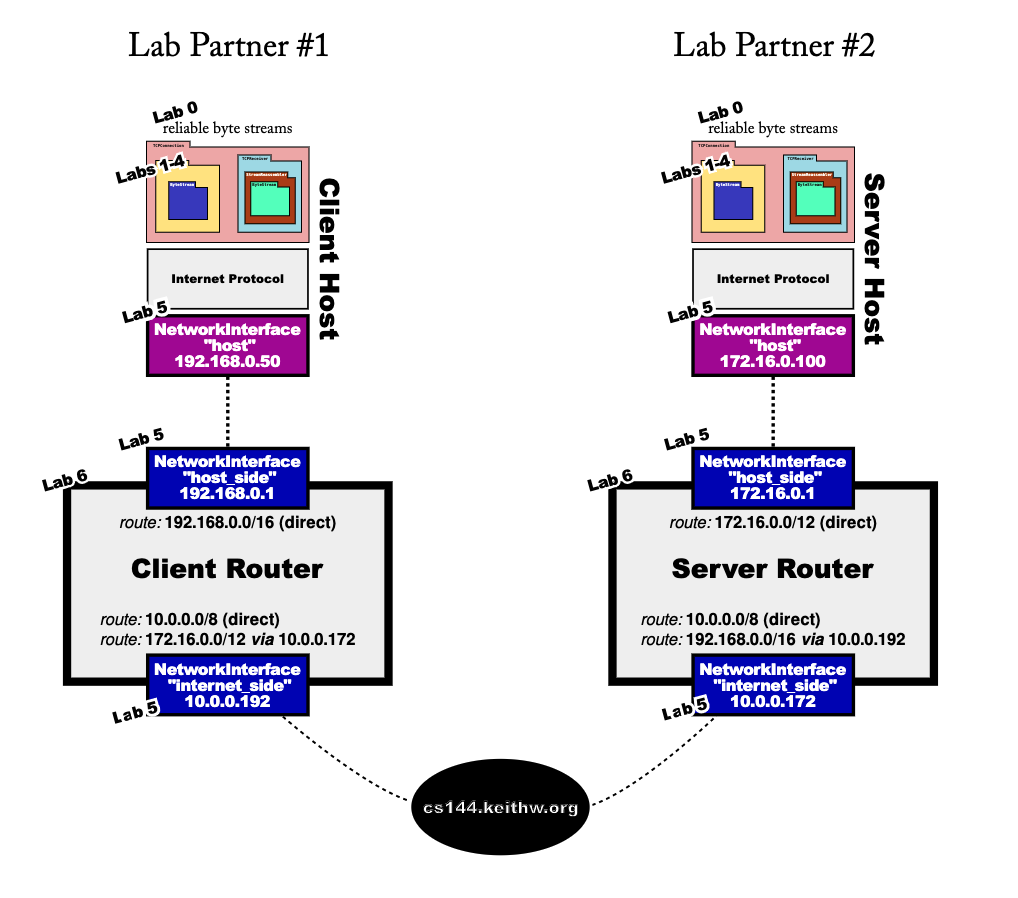

到此为止,您已经实现了Internet基础设施的很大一部分。从Lab0(一个可靠的字节流),到Labs 1-4(传输控制协议),Lab 5(一个IP /以太网网络接口)和 Lab 6(一个IP路由器),你已经做了大量的编码工作!

在这个实验室中,您不需要做任何编码(假设您之前的实验室处于合理的工作状态)。相反,为了结束你的成就,你将使用你之前的所有实验来创建一个真实的网络,其中包括你的网络堆栈(主机和路由器)与课堂上另一个学生实现的网络堆栈通信。

这个实验是两人一组做的。你需要和一个实验伙伴(班上的另一个学生)一起工作。请使用实验环节寻找实验伙伴,如果你不能参加实验环节,请使用广场。如果有必要,同一个学生可以多次担任“实验搭档”。

网络

在本实验中,您将创建一个真实的网络,将您的网络堆栈与课堂上另一个学生实现的网络堆栈结合起来。每个人贡献一台主机(包括可靠的字节流、TCP实现和networkinterface)和一台路由器:

第一个窗口:

1

| ./apps/lab7 server cs144.keithw.org 3000

|

第二个窗口:

1

| ./apps/lab7 server cs144.keithw.org 3000

|

make check

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

280

281

282

283

284

285

286

287

288

289

290

291

292

293

294

295

296

297

298

299

300

301

302

303

304

305

306

307

308

309

310

311

312

313

314

315

316

317

318

319

320

321

322

323

324

325

326

327

328

329

330

331

332

333

334

335

336

| [100%] Testing libsponge...

Test project /home/misaka/sponge/build

Start 1: t_wrapping_ints_cmp

1/164 Test

Start 2: t_wrapping_ints_unwrap

2/164 Test

Start 3: t_wrapping_ints_wrap

3/164 Test

Start 4: t_wrapping_ints_roundtrip

4/164 Test

Start 5: t_recv_connect

5/164 Test

Start 6: t_recv_transmit

6/164 Test

Start 7: t_recv_window

7/164 Test

Start 8: t_recv_reorder

8/164 Test

Start 9: t_recv_close

9/164 Test

Start 10: t_recv_special

10/164 Test

Start 11: t_send_connect

11/164 Test

Start 12: t_send_transmit

12/164 Test

Start 13: t_send_retx

13/164 Test

Start 14: t_send_window

14/164 Test

Start 15: t_send_ack

15/164 Test

Start 16: t_send_close

16/164 Test

Start 17: t_send_extra

17/164 Test

Start 18: t_strm_reassem_single

18/164 Test

Start 19: t_strm_reassem_seq

19/164 Test

Start 20: t_strm_reassem_dup

20/164 Test

Start 21: t_strm_reassem_holes

21/164 Test

Start 22: t_strm_reassem_many

22/164 Test

Start 23: t_strm_reassem_overlapping

23/164 Test

Start 24: t_strm_reassem_win

24/164 Test

Start 25: t_strm_reassem_cap

25/164 Test

Start 26: t_byte_stream_construction

26/164 Test

Start 27: t_byte_stream_one_write

27/164 Test

Start 28: t_byte_stream_two_writes

28/164 Test

Start 29: t_byte_stream_capacity

29/164 Test

Start 30: t_byte_stream_many_writes

30/164 Test

Start 31: t_webget

31/164 Test

Start 32: arp_network_interface

32/164 Test

Start 33: router_test

33/164 Test

Start 34: t_tcp_parser

34/164 Test

Start 35: t_ipv4_parser

35/164 Test

Start 36: t_active_close

36/164 Test

Start 37: t_passive_close

37/164 Test

Start 39: t_ack_rst

38/164 Test

Start 41: t_ack_rst_win

39/164 Test

Start 43: t_connect

40/164 Test

Start 45: t_listen

41/164 Test

Start 46: t_winsize

42/164 Test

Start 48: t_retx

43/164 Test

Start 49: t_retx_win

44/164 Test

Start 50: t_loopback

45/164 Test

Start 51: t_loopback_win

46/164 Test

Start 52: t_reorder

47/164 Test

Start 53: t_address_dt

48/164 Test

Start 54: t_parser_dt

49/164 Test

Start 55: t_socket_dt

50/164 Test

Start 56: t_udp_client_send

51/164 Test

Start 57: t_udp_server_send

52/164 Test

Start 58: t_udp_client_recv

53/164 Test

Start 59: t_udp_server_recv

54/164 Test

Start 60: t_udp_client_dupl

55/164 Test

Start 61: t_udp_server_dupl

56/164 Test

Start 62: t_ucS_1M_32k

57/164 Test

Start 63: t_ucS_128K_8K

58/164 Test

Start 64: t_ucS_16_1

59/164 Test

Start 65: t_ucS_32K_d

60/164 Test

Start 66: t_ucR_1M_32k

61/164 Test

Start 67: t_ucR_128K_8K

62/164 Test

Start 68: t_ucR_16_1

63/164 Test

Start 69: t_ucR_32K_d

64/164 Test

Start 70: t_ucD_1M_32k

65/164 Test

Start 71: t_ucD_128K_8K

66/164 Test

Start 72: t_ucD_16_1

67/164 Test

Start 73: t_ucD_32K_d

68/164 Test

Start 74: t_usS_1M_32k

69/164 Test

Start 75: t_usS_128K_8K

70/164 Test

Start 76: t_usS_16_1

71/164 Test

Start 77: t_usS_32K_d

72/164 Test

Start 78: t_usR_1M_32k

73/164 Test

Start 79: t_usR_128K_8K

74/164 Test

Start 80: t_usR_16_1

75/164 Test

Start 81: t_usR_32K_d

76/164 Test

Start 82: t_usD_1M_32k

77/164 Test

Start 83: t_usD_128K_8K

78/164 Test

Start 84: t_usD_16_1

79/164 Test

Start 85: t_usD_32K_d

80/164 Test

Start 86: t_ucS_128K_8K_l

81/164 Test

Start 87: t_ucS_128K_8K_L

82/164 Test

Start 88: t_ucS_128K_8K_lL

83/164 Test

Start 89: t_ucR_128K_8K_l

84/164 Test

Start 90: t_ucR_128K_8K_L

85/164 Test

Start 91: t_ucR_128K_8K_lL

86/164 Test

Start 92: t_ucD_128K_8K_l

87/164 Test

Start 93: t_ucD_128K_8K_L

88/164 Test

Start 94: t_ucD_128K_8K_lL

89/164 Test

Start 95: t_usS_128K_8K_l

90/164 Test

Start 96: t_usS_128K_8K_L

91/164 Test

Start 97: t_usS_128K_8K_lL

92/164 Test

Start 98: t_usR_128K_8K_l

93/164 Test

Start 99: t_usR_128K_8K_L

94/164 Test

Start 100: t_usR_128K_8K_lL

95/164 Test

Start 101: t_usD_128K_8K_l

96/164 Test

Start 102: t_usD_128K_8K_L

97/164 Test

Start 103: t_usD_128K_8K_lL

98/164 Test

Start 104: t_ipv4_client_send

99/164 Test

Start 105: t_ipv4_server_send

100/164 Test

Start 106: t_ipv4_client_recv

101/164 Test

Start 107: t_ipv4_server_recv

102/164 Test

Start 108: t_ipv4_client_dupl

103/164 Test

Start 109: t_ipv4_server_dupl

104/164 Test

Start 110: t_icS_1M_32k

105/164 Test

Start 111: t_icS_128K_8K

106/164 Test

Start 112: t_icS_16_1

107/164 Test

Start 113: t_icS_32K_d

108/164 Test

Start 114: t_icR_1M_32k

109/164 Test

Start 115: t_icR_128K_8K

110/164 Test

Start 116: t_icR_16_1

111/164 Test

Start 117: t_icR_32K_d

112/164 Test

Start 118: t_icD_1M_32k

113/164 Test

Start 119: t_icD_128K_8K

114/164 Test

Start 120: t_icD_16_1

115/164 Test

Start 121: t_icD_32K_d

116/164 Test

Start 122: t_isS_1M_32k

117/164 Test

Start 123: t_isS_128K_8K

118/164 Test

Start 124: t_isS_16_1

119/164 Test

Start 125: t_isS_32K_d

120/164 Test

Start 126: t_isR_1M_32k

121/164 Test

Start 127: t_isR_128K_8K

122/164 Test

Start 128: t_isR_16_1

123/164 Test

Start 129: t_isR_32K_d

124/164 Test

Start 130: t_isD_1M_32k

125/164 Test

Start 131: t_isD_128K_8K

126/164 Test

Start 132: t_isD_16_1

127/164 Test

Start 133: t_isD_32K_d

128/164 Test

Start 134: t_icS_128K_8K_l

129/164 Test

Start 135: t_icS_128K_8K_L

130/164 Test

Start 136: t_icS_128K_8K_lL

131/164 Test

Start 137: t_icR_128K_8K_l

132/164 Test

Start 138: t_icR_128K_8K_L

133/164 Test

Start 139: t_icR_128K_8K_lL

134/164 Test

Start 140: t_icD_128K_8K_l

135/164 Test

Start 141: t_icD_128K_8K_L

136/164 Test

Start 142: t_icD_128K_8K_lL

137/164 Test

Start 143: t_isS_128K_8K_l

138/164 Test

Start 144: t_isS_128K_8K_L

139/164 Test

Start 145: t_isS_128K_8K_lL

140/164 Test

Start 146: t_isR_128K_8K_l

141/164 Test

Start 147: t_isR_128K_8K_L

142/164 Test

Start 148: t_isR_128K_8K_lL

143/164 Test

Start 149: t_isD_128K_8K_l

144/164 Test

Start 150: t_isD_128K_8K_L

145/164 Test

Start 151: t_isD_128K_8K_lL

146/164 Test

Start 152: t_icnS_128K_8K_l

147/164 Test

Start 153: t_icnS_128K_8K_L

148/164 Test

Start 154: t_icnS_128K_8K_lL

149/164 Test

Start 155: t_icnR_128K_8K_l

150/164 Test

Start 156: t_icnR_128K_8K_L

151/164 Test

Start 157: t_icnR_128K_8K_lL

152/164 Test

Start 158: t_icnD_128K_8K_l

153/164 Test

Start 159: t_icnD_128K_8K_L

154/164 Test

Start 160: t_icnD_128K_8K_lL

155/164 Test

Start 161: t_isnS_128K_8K_l

156/164 Test

Start 162: t_isnS_128K_8K_L

157/164 Test

Start 163: t_isnS_128K_8K_lL

158/164 Test

Start 164: t_isnR_128K_8K_l

159/164 Test

Start 165: t_isnR_128K_8K_L

160/164 Test

Start 166: t_isnR_128K_8K_lL

161/164 Test

Start 167: t_isnD_128K_8K_l

162/164 Test

Start 168: t_isnD_128K_8K_L

163/164 Test

Start 169: t_isnD_128K_8K_lL

164/164 Test

100% tests passed, 0 tests failed out of 164

Total Test time (real) = 39.33 sec

[100%] Built target check

|